# Optimising the quality of gate dielectrics in Ge holespin qubit devices

## Simon Robson<sup>[1]</sup>

Ming Ni<sup>[1]</sup>, Andrea Ballabio<sup>[2]</sup>, Daniel Chrastina<sup>[2]</sup>, Giovanni Isella<sup>[2]</sup>, Georgios Katsaros<sup>[1]</sup>

<sup>[1]</sup> Institute of Science and Technology Austria, Am Campus 1, A-3400 Klosterneuburg

<sup>[2]</sup> L-NESS, Physics Department, Politecnico di Milano, via Anzani 42, 22100, Como, Italy

#### simon.robson@ista.ac.at

Continued advances in the fabrication of Ge/SiGe heterostructures have led to gatedefined hole spins in strained germanium layers being identified as a viable qubit platform [1, 2]. Advantages include a large spin-orbit interaction to allow all-electric control of the spin, a small effective mass to allow a more relaxed gate layout geometry, and a p-like orbital symmetry giving a reduced hyperfine interaction and thus favouring spin coherence. However, as the number of qubits is scaled up, increased focus on the uniformity of the device is required, whereby electrically-active defect states in the bulk and at interfaces can affect transport and introduce significant sources of decoherence [3, 4]. Careful control and optimisation of the device production process, including feedback loops at various fabrication stages, is thus an important task for qubit scale-up.

Here, we present outcomes from a series of experiments that focus on the role of the oxide as a medium for the trapping and emission of mobile charge carriers and thus contributing a significant source of charge noise. In the initial phase of investigation, test structures comprised of metal-oxidesemiconductor (MOS) capacitors on Si are used to evaluate the magnitude of fixed oxide charge Q<sub>f</sub> and interface trap density show that through We careful Dit. optimisation of the atomic layer deposition parameters, as well as incorporating various pre- and post-oxidation treatments, D<sub>it</sub> and Q<sub>f</sub> can be reduced below 2x10<sup>11</sup> eV<sup>-1</sup> cm<sup>-2</sup> and 1x10<sup>12</sup> cm<sup>-2</sup>, respectively. Next, we move to a Geo.7/SiGeo.3 substrate, the heterostructure stack used for quantum dot devices. In addition to MOS capacitors, we fabricate test structures comprising multiple depletion gates in order to probe charge disorder on the nanoscale. Here we show the benefits that post-oxidation and postmetallisation annealing bring in terms of reduced hysteresis and increased uniformity of the pinch-off voltages. All together, these results point to an optimised fabrication process flow that reflects a minimum in the amount of electrically-active defect states and thus a favourable environment for which to host large-scale qubit arrays in a relatively noise-free setting.

## References

- [1] G. Scappucci et al., Nature Reviews Materials 6(10) (2021) pp. 926-943

- [2] D. Jirovec et al., Nature Materials, 20(8) (2021) pp.1106-1112

- [3] M. J. Carballido et al., arXiv:2404.07313 (2024)

- [4] N. Sangwan et al., arXiv:2411.03995 (2024)

### Figures

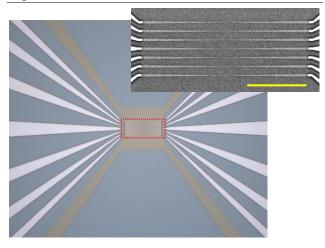

**Figure 1:** Optical/SEM images of a test structure comprising 7x Ti/Pd depletion gates fabricated on a Ge/SiGe substrate. Scale bar = 5  $\mu$ m