# Steps towards variability-resilient spin qubits

#### Biel Martinez<sup>1</sup>

Silvano DeFranceschi<sup>2</sup>, Yann-Michel Niquet<sup>3</sup>

- 1. Univ. Grenoble Alpes, CEA, LETI, F-38000, Grenoble, France

- 2. Univ. Grenoble Alpes, CEA, Grenoble INP, IRIG-PHELIQS, F-38000, Grenoble, France

- 3. Univ. Grenoble Alpes, CEA, IRIG-MEM-L\\_Sim, F-38000, Grenoble, France

#### biel.martinezidiaz@cea.f

The scalability of semiconductor spin qubits will undoubtedly face the challenge of ensuring clean enough environments to host qubits with homogeneous properties all across the quantum processors. In this sense, epitaxial heterostructures appear advantageous with respect to MOS-based counterparts [1] due to the crystalline nature of their interfaces. Holes in Ge/SiGe heterostructures experience a wide variety of SOC mechanisms [2-4], which can be leveraged for electrical spin manipulation, but also enhance the sensitivity to electrical disorder [5].

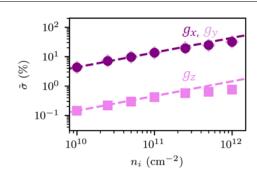

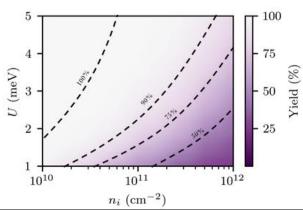

In this work, we performed numerical simulations to quantify the variability on the charge and spin properties of Ge spin qubits, evaluate its impact on the scalability perspectives of this platform, and explore actions to mitigate it. While variations in the charge properties remain moderate, spin properties still suffer from significant variability (see Figure 1). Nonetheless, the bounds for interface quality are highly constraining for large-scale architectures (see Figure 2). We showe that these constraints could be released via strain engineering [6] and gate lavout optimisation [7], reaching manageable variability levels at achievable interface qualities.

### References

[1] B. Martinez et. al. Phys. Rev. Applied 17, 024022 (2022)

- [2] B. Martinez et. al. Phys. Rev. B 106, 235426 (2022)

- [3] JC. Abadillo-Uriel *et. al.* Phys. Rev. Lett. 131, 097002 (2023)

- [4] EA. Rodriguez-Mena et. al. Phys. Rev. B 108, 205416 (2023)

- [5] B. Martinez et. al. Manuscript in preparation

- [6] B. Martinez et. al. Phys. Rev. Applied 22, 024030 (2024)

- [7] L. Mauro et. al. arXiv:2407.19854 (2024)

## **Figures**

**Figure 1:** Relative standard deviation of the inplane  $(g_x, g_y)$  and out-of-plane  $(g_z)$  effective g factors as a function of the charge trap density  $(n_i)$  at the top SiGe interface of a prototypical Ge spin qubit device.

**Figure 2:** Predicted percentage of devices with single-hole occupancy as a function of the charge trap density  $(n_i)$  and the qubits charging (U) energy in a device with shared plunger gate voltages.