# Silicon Nanowires with Quantum Dots for experimentation in Quantum Technologies

J Llobet<sup>1</sup>, J. Antoja<sup>1</sup>, X Borrisé<sup>2</sup>, D Bricio<sup>1</sup>, A. del Moral<sup>1</sup>, M Duch<sup>1</sup>, S Durán<sup>1</sup>, A Garcia<sup>1</sup>, A Guerrero<sup>1</sup>, R. Mas<sup>1</sup>, J Sanchez<sup>1</sup>, J Bausells<sup>1</sup>, **F Pérez-Murano<sup>1</sup>**

- <sup>1</sup> Institute of Microelectronics of Barcelona (IMB-CNM CSIC), Bellaterra, 08193, Spain

- <sup>2</sup>Catalan Institute of Nanoscience and Nanotechnology (ICN2), CSIC and BIST, Bellaterra, 08193, Catalonia, Spain

## Francesc.Perez@csic.es

## Abstract

Silicon Nanowires (SiNWs) are one of the building blocks for the development of semiconductor spin qubits based on quantum dots. We are developing a platform based on novel nanofabrication approaches following two mix and match routes: i) optical and electron beam lithography (EBL); ii) EBL and focused ion beam (FIB) implantation. The platform is designed for allowing rapid experimentation of novel device concepts.

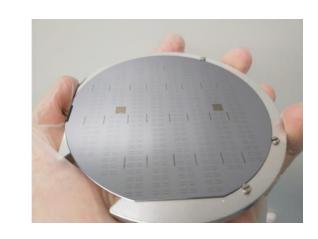

The first mix-and-match approach consists of 5 lithographic steps combining optical lithography and EBL using the same negative resist. The process allows to define more than 5000 individually connected SiNW devices (figure 1).

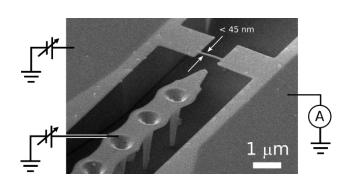

The second approach is based on a threestep fabrication scheme [1,2] using FIB implantation as a resistless lithography process followed by wet chemical etching. It allows to obtain suspended and not suspended silicon nanowires of sub-20 nm width. By the development of an annealing step, it is demonstrated the recovery of the electrical conduction up to four orders of magnitude, the out-diffusion of gallium and the promotion of nanocrystals (sub-10nm) embedded and constricted inside the silicon nanostructures [3,4]. The nanocrystalline nature of the resulting SiNWs allowed the development of single hole transistors (SHoTs)] as depicted in figure 2.

## References

- J. Llobet et al. J. Micro/Nanolith. MEMS MOEMS vol. 14 031207 (2015).

- [2] J. Llobet et al. Nanotechnology 25, 135302 (2014). Authors, Journal, Issue (Year) page

- [3] J. Llobet et al. Applied Physics Letters 107, 073104 (2015).

- [4] J. Llobet et al. Nanotechnology 29, 155303 (2018).

## Figures

**Figure 1:** Photograph of a 100 mm wafer containing more than 5,000 connected silicon nanowires

**Figure 2:** SEM image of a single hole transistor fabricated by a three step rapid prototyping process based on focused ion beam [4]