## Direct Metal Etch and Semi-Damascene Integration of Ruthenium: A Game-changer for interconnects

## <u>Giulio Marti\*</u>, Gayle Murdoch, Gilles Delie, Ankit Pokhrel, Anshul Gupta, Stefan Decoster, Souvik Kundu, Seongho Park, Zsolt Tokei *Imec, Kapeldreef 75, 3001 Heverlee, Belgium e-mail:* <u>giulio.marti@imec.be</u>

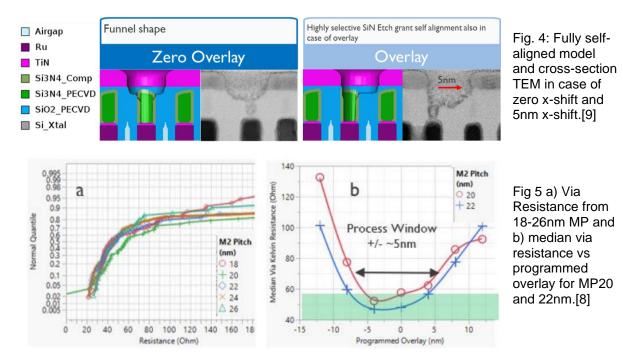

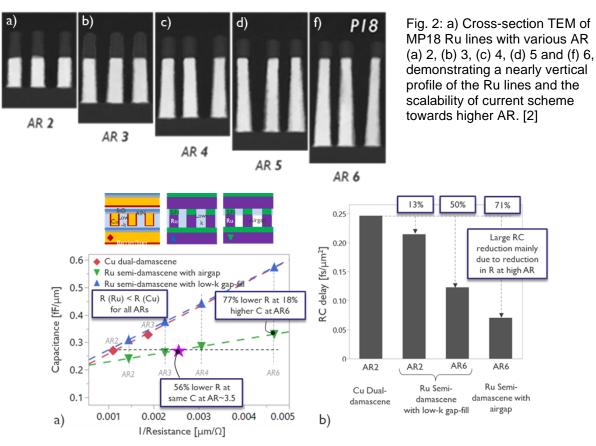

Alternative materials and integration processes as a replacement for Cu Dual Damascene have long been under scrutiny within the interconnect research communities. Reducing resistance and capacitance stands as a pivotal challenge in enhancing interconnect performance for forthcoming technology nodes. Ruthenium (Ru) emerges as a resilient contender at the metal level, diverging from Cu, owing to its resistance to oxidation, elevated melting point, low bulk resistivity [1], and the absence of a necessary metal barrier. Additionally, Ru facilitates subtractive metal semi-damascene (Fig.1) with notable integration advantages: (1) direct metal etch enables high aspect ratio (AR) patterning (Fig.2). This alleviates the constraints associated with trench filling, permitting resistance reductions at equivalent metal pitch (MP) [2,3] (Fig.3). (2) This methodology affords precise control over the height of patterned lines by adjusting the thickness of the deposited metal and the etch process, removing the need for a metal CMP [4,5]. (3) Below 22nm MP, a fully self-aligned via (Fig.4) becomes imperative to prevent via-to-line leakage [6,7].

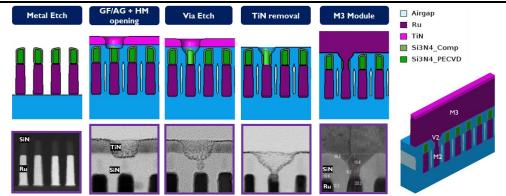

This proposed scheme utilizes a semi-damascene integration sequence: the first metal layer is formed through subtractive metal etching. Subsequently, a highly selective etching process is employed to construct the via on top of a lower metal line by removing its hard mask (HM). The next metal level is then established using subtractive metal etching. A pioneering demonstration of 2-metal level (2ML) devices using subtractive metal etch with Fully Self-Aligned Via (FSAV) was presented by Murdoch et al. [8] (Fig.5). Subsequent enhancements in etch and cleaning procedures laid the groundwork for the subsequent implementation FSAV high yielding [9]. In this presentation, we will delve into the intricate details of utilizing subtractive patterning with Ruthenium to implement the semi-damascene scheme—an innovative approach recommended by imec as a viable alternative to Copper (Cu) damascene in advanced logic nodes.

References

- 1. L. G. Wen et al., Proc. IEEE IITC/AMC 2016, May, 2016, pp. 34–36.

- 2. A. Pokhrel et al., "MP18–26 Ru Direct-Etch Integration Development with Leakage Improvement and Increased Aspect Ratio," IITC 2022;

- 3. A. Gupta et al., "Two-metal-level semi-damascene interconnect at metal pitch 18 nm and aspect-ratio 6 routed using fully self-aligned via", IEDM 2023

- 4. A. Gupta et al., 2018 IEEE IITC, 2018, pp. 4-6, doi: 10.1109/IITC.2018.8430415.

- 5. G. Murdoch et al., "Semidamascene Interconnects for 2nm node and Beyond," IITC 2020;

- 6. Murdoch et al "Feasibility study for fully aligned via for 5nm node", IITC 2018;

- 7. Chen et al., "Fully self-aligned via integration for interconnect scaling beyond 3nm node", IEDM 2021

- 8. Murdoch et al., "First demonstration of Two Metal Level Semi-damascene Interconnects with Fully Selfaligned Vias at 18MP", VLSI 2022

- **9.** G. Marti et al., "Two-level Semi-damascene interconnect with fully self-aligned Vias at MP18", IITC/MAM 2023

Fig. 1: Integration scheme for semi-damascene 2ML FSAV.[9]

Fig. 3 3-metal-level TCAD evaluation comparing Cu-dual damascene (DD) vs Ru-Semi-damascene (SD). (a) Compared to AR2 Cu-DD, AR2 Ru-SD with airgap offers a significant, 24% lower C, while AR6 Ru-SD with airgap have comparable C. (b) RC delay product shows 13% lower RC with Ru semi-damascene thanks to lower film resistivity and barrierless Ru compared to Cu with 2 nm barrier/liner. Possibility to fabricate high aspect ratio Ru lines with airgaps in semi-damascene can lower the RC further by 71%. TCAD evaluation is carried out using imec resistivity model [9] on 10 nm width and MP18 nm 3-metal configuration as shown in the schematics.[3]