## **Tianran Li** Jinxiong Wu; Congwei Tan; Teng Tu; Hailin Peng College of Chemistry and Molecular Engineering, Peking University, No.202 Chengfu Rd., Beijing, China

litr-cnc@pku.edu.cn

## Chemical patterning and device integration of 2D Bi<sub>2</sub>O<sub>2</sub>Se

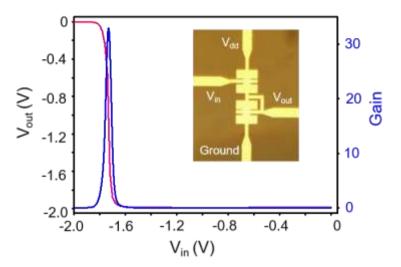

2D semiconductor has been viewed as potential competitor of silicon due to its atomic thickness which is naturally resistant to short channel effect. However, lack of consistency has post a serious limitation on future application of 2D semiconductors. Up to now, most researchers focus on fabricating isolated transistors and evaluate their device performance. In 2017, Wu et al. synthesized a ternary 2D semiconductor[1] Bi<sub>2</sub>O<sub>2</sub>Se which has shown high electron mobility(~450 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and excellent stability against oxygen and moisture. Meanwhile, the authors demonstrated highly efficient chemical patterning of 2D Bi<sub>2</sub>O<sub>2</sub>Se and successfully fabricated photodetector arrays[2]. Based on these researches, we are now able to fabricate logic circuits on wet-etched CVD Bi<sub>2</sub>O<sub>2</sub>Se samples. Figure.1 shows V<sub>in</sub>-V<sub>out</sub> curve on thus fabricated inverter. These devices could work in 2V and gain is over 30. More complex circuits are also available.

## References

- [1] Wu, Jinxiong, et al. Nature nanotechnology 12.6 (2017): 530.

- [2] Wu, Jinxiong, et al. Advanced Materials 29.44 (2017): 1704060.

## Figures

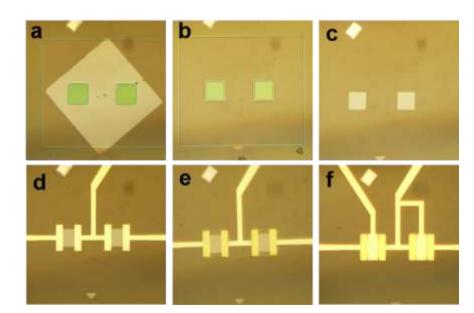

**Figure 1:** Schematic illustration of fabricating Bi<sub>2</sub>O<sub>2</sub>Se logic gate. (a) EBL pattering of original sample. (b) Chemical etching of exposed region. (c) Removing PMMA mask. (d) Depositing of S-D electrodes. (e) ALD HfO<sub>2</sub> for gate dielectric. (f) Depositing of gate electrodes and interconnect.

Figure 2: Performance of inverter circuit built on wet-etched 2D-Bi2O2Se.