## ZhengMing Wu<sup>2</sup>

Colin Rawlings<sup>2</sup>, Simon Bonanni<sup>2</sup>, Martin Spieser<sup>2</sup>, Philipp Mensch<sup>1</sup>, Siegfried Kang<sup>1</sup>, Heiko Wolf<sup>1</sup>, Armin Knoll<sup>1</sup>

<sup>1</sup>IBM Research – Zurich, Saeumerstrasse 4, 8803 Rueschlikon, Switzerland

<sup>2</sup>SwissLitho AG, Technoparkstrasse 1, 8005 Zurich, Switzerland

wu@swisslitho.com

# Fabrication of sub-20 nm Metal Electrodes on 2D Materials without a Charged Particle Beam

#### Abstract

Charged particle beams for the fabrication of devices comprising sensitive nanowires or 2D materials often lead to unwanted influence or damage of electronic properties of the device [1]. Still, electron beam lithography (EBL) in combination with lift-off is the most commonly used method to fabricate prototypes of such devices.

Thermal Scanning Probe Lithography (t-SPL) [2, 3] is an alternative mask-less lithography technique which is also commercially available since 2014. It provides similar speed (up to 20 mm/s) and resolution (10 nm half-pitch) as EBL, but without charged particles involved. Here, we present two recently developed lift-off techniques for t-SPL that have enabled the creation of complex sub-20 nm Au, Pt and Ni structures and devices without the usage of high energy charged particle beams [4].

Thermal Scanning Probe Lithography (t-SPL) uses a heated silicon tip to locally decompose and evaporate a thermally responsive resist [5], usually PPA (polyphthalaldehye). A two-layer or three-layer process in combination with wet or dry etching is demonstrated to create a suitable under-cut for lift-off, respectively. During the t-SPL process the heated tip only influences the top PPA layer and leaves the underlying substrate unharmed. This is in contrast to beam based technologies like EBL or Focused Ion Beam (FIB) where most of the energy is actually deposited in the substrate and vacancies in graphene or other 2D materials can be created.

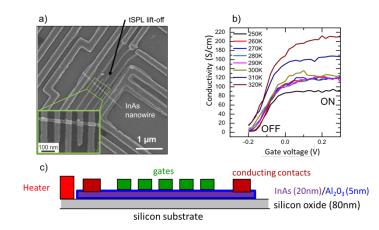

We demonstrate the capabilities of the new t-SPL lift-off processes by fabrication of transistors with improved performance (See Figure 1). 50 nm wide fingered top gates have been fabricated with nanometer overlay accuracy. The superb switching behavior of the transistor shows the absence of trapped charge in the gate oxide, which usually occurs during EBL fabrication of such devices and prevents proper device operation.

#### ACKNOWLEDGMENTS:

We thank P. Mensch and S. Karg for providing InAs nanowires and performing the transport measurements, U. Drechsler for cantilever fabrication, and R. Allenspach and W. Riess for fruitful discussions. The research leading to these results received funding from European Union's Seventh Framework Program FP7/2007-2013 under Grant Agreement No. 318804 (SNM).

#### References

- [1] S. F. Karg, V. Troncale, U. Drechsler, P. Mensch, P. Das Kanungo, H. Schmid, V. Schmidt, L. Gignac, H. Riel, B. Gotsmann, Nanotechnology 25 (2014), 305702.

- [2] D. Pires, J.L. Hedrick, A. de Silva, J. Frommer, B. Gotsmann, H. Wolf, M. Despont, U. Duerig, A.W. Knoll, Science 328 (2010), 732-735

- [3] P.C. Paul, A.W. Knoll, F. Holzner, M. Despont, U. Duerig, Nanotechnology 22 (2011), 275306.

- [4] H. Wolf, C. Rawlings, P. Mensch, J.L. Hedrick, D.J. Coady, U. Duerig and A. Knoll, J. Vac. Sci. Technol. B 33 (2015), 02B102.

[5] C. Aso, S. Tagami and T. Kunitake, J. Polym. Sci. A-1 (1969), 497-511.

### Figures

**Figure 1:** a) The gate electrodes of InAs nanowire transistor fabricated using the tSPL and lift-off. b) Switching behavior of the transistor. c) Schematic of the InAs nanowire transistor.