## Tomoaki Oba

Takamasa Kawanago, Shunri Oda

QNERC and Dept. of EE., Tokyo Institute of Technology, 2-12-1-S9-12, Ookayama, Meguro-ku, 152-8550, Tokyo, Japan

oba.t.ae@m.titech.ac.jp

# Gated Four-Probe Method for Evaluation of Electrical Characteristics in MoS<sub>2</sub> Field-Effect Transistors

Layered semiconductor of transition metal dichalcogenides (TMDC) has been considerable attention because of their various properties [1]. New classes of semiconductor materials motivate an investigation of carrier mobility and contact resistance in field-effect transistor configuration from the view point of both scientific interests and practical applications. This study describes the gated four-probe method to evaluate the relation between interfacial properties and channel mobility in MoS<sub>2</sub> FETs [2, 3].

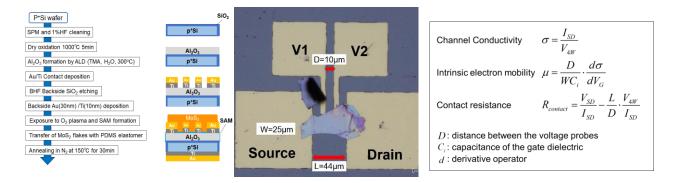

Heavily-doped p\*-type Si wafer was subjected to SPM and 1% HF cleaning. Thermal SiO<sub>2</sub> was grown by dry oxidation at 1000 °C for 5 min. Subsequently, Al<sub>2</sub>O<sub>3</sub> was deposited by ALD (TMA, H<sub>2</sub>O, 300 °C) on SiO<sub>2</sub>. Au (40 nm)/Ti (10 nm) was deposited by thermal evaporation and lift-off for source/drain contact and two potential probes. After removal of back side SiO<sub>2</sub> with BHF, Au (30 nm) / Ti (10 nm) for back gate contact was deposited on the back side of the substrate by thermal evaporation. Next, the substrate was subjected to oxygen plasma to form hydroxyl groups on the surface of Al<sub>2</sub>O<sub>3</sub>. Then, the substrate was immersed into 2-propanol containing 5 mM n-octadecylphosphonic acid (ODPA) for 4 hours at room temperature [4]. Annealing was conducted at 100 °C in N<sub>2</sub> for 30 min to stabilize ODPA. The gate dielectric consists of hybrid ODPA/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>. Mechanically exfoliated MoS<sub>2</sub> were transferred to the substrate with the PDMS elastomer. Finally, devices were annealed in N<sub>2</sub> at 150 °C for 30 min to improve source/drain contact. The fabrication process and device structure are summarized in Fig. 1. Fig.2 shows microscope image of fabricated FET.

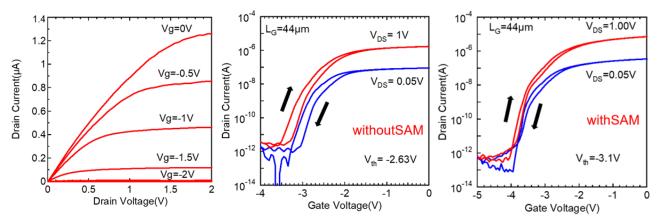

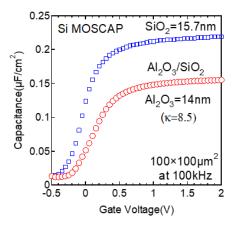

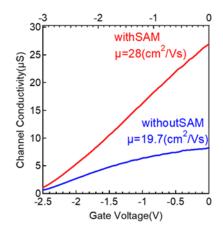

The channel mobility were evaluated with four-probe method based on the equations, as shown in Fig. 3. Fig. 4 shows the representative  $I_d$ - $V_d$  characteristics of  $MoS_2$  FET with gated four-probe method. The FET operation was observed with this four-probe configuration. Fig. 5 shows the representative  $I_d$ - $V_g$  characteristics of  $MoS_2$  FET without SAM. Hysteresis in clockwise direction was observed. On the other hand, formation of SAM can suppress the hysteresis in  $I_d$ - $V_g$  characteristics as shown in Fig. 6. The channel potential was estimated during  $I_d$ - $V_g$  measurement using internal two probes between source and drain contact. Fig. 7 shows the C-V characteristics of Si MOSCAP for  $SiO_2$  and  $AI_2O_3/SiO_2$  gate dielectric. The physical thickness of  $SiO_2$  was 15.7 nm. The physical thickness of  $AI_2O_3$  corresponds 14 nm when the dielectric constant of  $AI_2O_3$  was assumed to be 8.5. Also, the physical thickness and dielectric constant of  $AI_2O_3$  was assumed to be 8.5. Also, the physical thickness and dielectric constant of  $AI_2O_3$  was assumed to observe the overall capacitance of  $AI_2O_3/SiO_2$  is 0.13  $\mu$ m/cm². Fig. 8 shows  $AI_3$ 0 dependence of four-probe conductivity ( $AI_3$ 0). The channel mobility ( $AI_3$ 1) was evaluated from the  $AI_3$ 2 using the equation as shown in Fig. 3. The  $AI_3$ 3 with SAM is improved as high as 28 cm²/ $AI_3$ 5 while the  $AI_3$ 4 without SAM shows 19.7 cm²/ $AI_3$ 5 while the  $AI_3$ 5 representative  $AI_3$ 5 representa

#### **Acknowledgments**

The authors would like to thank Prof. Y. Kawano, Prof. K. Kakushima, Prof. H. Wakabayashi, and Prof. K. Tsutsui of Tokyo Institute of Technology for their continuous support in the experiments. This study was supported by JST-CREST (Grant No. JPMJCR16F4), JSPS Grant-in-Aid for Young Scientists (B) (Grant No. 17K14662) and Yazaki Memorial Foundation for Science and Technology.

#### References

- [1] B.Radisavljevic et al., Nat. Nanotechnol. 6, 147 (2011).

- [2] V. C. Sundar et al., Science, 303, 12, 1644 (2004).

- [3] V. Podzorov et al. Appl. Phys. Lett., 84, 3301 (2004).

- [4] T. Kawanago et al., Appl. Phys. Lett. 108, 041605 (2016).

### **Figures**

Figure 1: Fabrication process and device structure.

Figure 2: Microscope image of fabricated FET.

Figure 3: Equations to evaluate channel mobility & contact resistance with gated four-probe method.

Figure 4: Representative I<sub>d</sub>-V<sub>d</sub> characteristics of MoS<sub>2</sub> FET with gated four-probe method.

5: Bidirectional **Figure** characteristics  $MoS_2$ without SAM.

$I_{d}$ - $V_{g}$ **Figure** 6: Bidirectional characteristics of MoS<sub>2</sub> FET with SAM.

Figure 7: C-V characteristics of Si MOSCAP for SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate dielectric.

FET

Figure 8: Impact of SAM on channel mobility estimated by fourprobe method.