## Faisal Ahmed<sup>1</sup>

Min Sup Choi<sup>2,3</sup>, Youg Duck Kim<sup>3</sup>, James Hone<sup>3</sup> and Won Jong Yoo<sup>1,2,\*</sup>

<sup>1</sup>School of Mechanical Engineering, Sungkyunkwan University, Suwon, Korea.

<sup>2</sup>Department of Nano Sciences, Sungkyunkwan University, Suwon, Korea.

<sup>3</sup>Department of Mechanical Engineering, Columbia University, New York, USA.

yoowj@skku.edu

# Study of High Electric Field Breakdown Thermometry in Black Phosphorus Field Effect Transistor

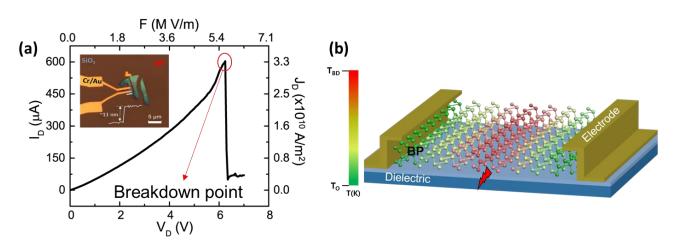

The re-introduction of two-dimensional (2D) layered black phosphorus (BP) as a channel material for solid state electronic applications has excited significant interest due to its versatile properties.[1-3] BP is considered as a favorable candidate material for electronics and opto-electronic applications becasue it has thickness dependent direct band gap, strong in-plane anisotropy and high carrier mobility.[1,3] But its thermal conductivity is smaller (k~25 W/m.K) as compared to other 2D materials like graphene and MoS<sub>2</sub>, that is good for thermoelectric applications but it causes thermal spreading problems specially at higher applied electric field.[2,5,6] Therefore, we study the heat dissipation in multilayer BP FET using highly robust electrical breakdown approach, in which the applied bias is gradually escalated to the point that physical breakdown occurs. Our measured 11 nm thick BP device (inset of Fig. a) exhibits a high current density of ~3.5×10<sup>10</sup> A/m<sup>2</sup> that is ~ one order of magnitude higher than achieved by multilayer MoS<sub>2</sub>. Interestingly, at high electrical field breakdown region, an unusual liner I-V curve was observed instead of current saturation as shown in Fig. a, perhaps due to new carrier generation due to impact ionization of accelerated charged carriers. By adopting a robust size dependent electro-thermal transport model, we extract interfacial thermal conductance of 1~10 M W/K.m<sup>2</sup> for BP-dielectic interfaces. Finally, based on our findings, we realized that most of the thermal power is deposited along the BP-SiO<sub>2</sub> interface while electrodes serve as efficient heat sink in operational BP FETs (Fig. b), thus an efficient thermal spreading is realized via dielectric engineering. Our results provide important figureof-merits and information related to electrical breakdown and power dissipation in BP FET that are highly crucial for the design, reliability and integration of novel 2D materials for energy efficient circuits and systems.

### References

Liu H., et al. ACS Nano, 6, (2014) 8563-8569. [2] Engel M., et al., Nat. lett., 15, (2015) 6785-6788.

Li, L., et al. Nat. Nanotech. 10, (2015) 608-613. [4] Dewu Y., et al., Nanoscale, 8, (2016) 12773.

Pop, E., Nano Research, 3, (2010) 147-169. [6] Ahmed F., et al. Adv. Funct. Mater., (2017) 1604025.

### Figures

**Figure 1: (a)** I-V plot of multilayer back gate BP device at high applied drain bias (V<sub>D</sub>), where red circle indicates breakdown point. (b) The schematic of thermal spreading in BP device.

#### ACKNOWLEDGEMENTS

This work was supported by the Global Research Laboratory (GRL) Program (2016K1A1A2912707) and Global Frontier R&D Program (2013M3A6B1078873) at the Center for Hybrid Interface Materials (HIM), both funded by the Ministry of Science, ICT & Future Planning *via* the National Research Foundation of Korea (NRF).