# Device design parameters for carbon nanotube field-effect transistors

## Aníbal Pacheco-Sánchez<sup>1</sup>

Michael Schröter<sup>1,2</sup>

<sup>1</sup>Chair for Electron Devices and Integrated Circuits, Technische Universität Dresden, 01062, Dresden, Germany.

<sup>2</sup>ECE Department, University of California, San Diego, CA 92103, U.S.A.

Anibal.Pacheco-Sanchez@tu-dresden.de

## Abstract

Among the extraordinary electrical characteristics, such as low scattering rate and high current-carrying capability, the intrinsic linearity of carbon nanotube (CNT) field effect transistors (CNTFETs) is expected to be beneficial for future high-frequency (HF) applications once the device is optimized [1], [2]. Performance projection studies [3] and fabricated proof-of-concept HF circuits [4]-[6] have shown the feasibility of CNTFETs for HF applications. Some technology related issues can be overcome by sophisticated techniques [7] and an adequate device characterization [8]. However, modeling and technology groups efforts are developed towards an optimized device suitable for mass production. An important performance parameter of the transport properties of the channel, such as the mobility, helps the device optimization. In addition, the metal-CNT interfaces, key factors limiting the device performance, need to be properly characterized by a Schottky barrier and a contact resistance in order to improve the current injection [9], [10]. A review on concepts and extraction methods of Schottky barrier height, contact resistance and mobility for carbon nanotube field-effect transistors (CNTFETs) is presented. The methods are applied to synthetic and experimental data of singleand multi-tube CNTFETs with short- and longchannel lengths obtained by our group [8], [11], [12].

### References

- [1] M. Schröter et al., IEEE J. Electron Devices Soc., 1(1), 2013, 9-20.

- [2] S. Mothes et al., IEEE Trans. Nanotechnol., 15(2), 2015, 372-378.

- [3] M. Claus et al., in Proc. SBMO/IEEE MTT-S Int. Microw. Optoelectron. Conf., 2015.

- [4] M. Eron et al., IEEE Electron. Lett., 47(4), 2011, 265-266.

- [5] A. Taghavi et al., in Proc. SBMO/IEEE MTT-S Int. Microw. Optoelectron. Conf., 2015.

- [6] A. Taghavi et al., IEEE Microw.Compon. Lett., 27(6), 2017, 578-580.

- [7] J. Tittmann et al., IEEE/ACM International Symposium on Nanoscale Architectures, 2014.

- [8] M. Haferlach et al., IEEE Trans. Nanotechnol., 15(4), 2016, 619-626.

- [9] A. Pacheco-Sanchez et al., Solid-State Electron., 125, 2016, 161-166.

- [10] A. Pacheco-Sanchez et al., Appl. Phys. Lett., 111, 2017, 163108.

- [11] M. Claus et al., J. Comput. Electron., 13(3), 2014, 689-700.

- [12] M. Schröter et al., IEEE Trans. Electron. Dev., 62(1), 2015, 52-60.

### Figures

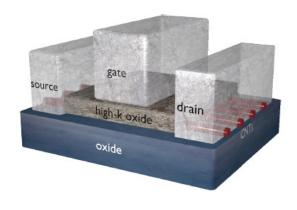

Figure 1: Top gate multitube CNTFET