# Towards Wafer Scale Integration of CVD Graphene and 2D Materials

## Max C. Lemme

RWTH Aachen University, Chair of Electronic Devices, Otto-Blumenthal-Str. 2, 52074 Aachen, Germany

AMO GmbH, Otto-Blumenthal-Str. 25, 52074 Aachen, Germany

#### lemme@amo.de

#### Abstract

Key to commercial uptake of twodimensional (2D) materials in electronics is the availability of scalable manufacturing and integration processes. Since a disruptive replacement of existing technology is unlikely at this point, 2D process technology should be compatible with conventional semiconductor manufacturing. While wafer scale production of graphene and 2D materials is feasible by chemical vapor deposition and related methods, the transfer of such grown layers to target substrates still faces severe challenges. In addition, defining and controlling quality, yield and reproducibility of (opto-)electronic devices is at a very early stage. This presentation will discuss approaches to graphene wafer scale integration, including yield and reliability tests of electronic devices [1], [2] and wafer scale integrated photodetectors [3]. It will also discuss device integration of the group ten material platinum diselenide (PtSe<sub>2</sub>), which can be grown from thin platinum films at 400°C and below [4].

### References

A. D. Smith, S. Wagner, S. Kataria, B.

G. Malm, M. C. Lemme, M. Östling, "Wafer-Scale Statistical Analysis of Graphene FETs, Part I: Wafer-Scale Fabrication and Yield Analysis," *IEEE Trans. Electron Devices*, vol. 64, no. 9, pp. 3919–3926, Sep. 2017.

A. D. Smith, S. Wagner, S. Kataria, B.

G. Malm, M. C. Lemme, and M. Östling, "Wafer-Scale Statistical Analysis of Graphene Field-Effect Transistors, Part II: Analysis of Device Properties," *IEEE Trans. Electron Devices*, vol. 64, no. 9, pp. 3927– 3933, Sep. 2017.

[3] D. Schall, C. Porschatis, M. Otto, and D. Neumaier, "Graphene photodetectors with a bandwidth > 76 GHz fabricated in a 6" wafer process line," J. Phys. Appl. Phys., vol. 50, no. 12, p. 124004, 2017.

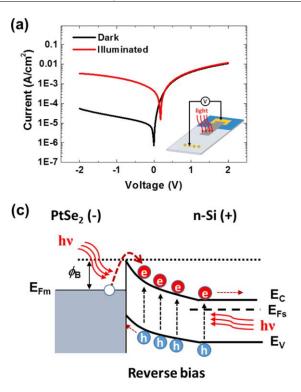

[4] C. Yim *et al.*, "High-Performance Hybrid Electronic Devices from Layered PtSe<sub>2</sub> Films Grown at Low Temperature," ACS Nano, vol. 10, no. 10, pp. 9550–9558, Oct. 2016.

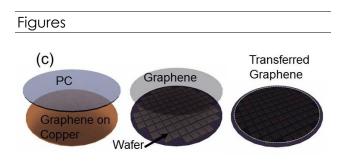

Figure 1: Wafer scale transfer of graphene (adapted from [1]).

**Figure 2:** PtSe<sub>2</sub> – silicon Schottky diode and operation principle (adapted from [4])