# GrapheneforUS

### **MD MAHFUZUR RAHMAN<sup>1</sup>**

Amirjan Bin Nawabjan<sup>2</sup> Department of Nano-Micro Engineering, Universiti Teknologi Malaysia, 81310 Skudai, Johor, MALAYSIA

mrmd4@graduate.utm.my

## Doped Graphene on Silicon FET for High Drain Current and Applications in RF And Logic Circuits

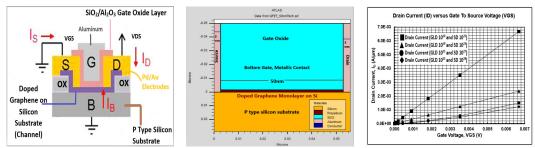

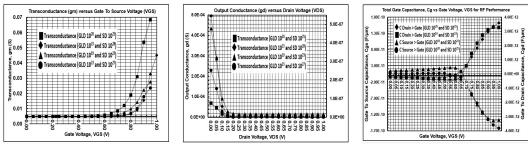

The Si-adsorbed and Si-substituted monolayer Si-doped graphene (Si:Gr) material has a range of structural and electronic features, according to recent researches. The Si:Gr demonstrates adatom-diversified geometric structure, silicon-carbon dominated energy bands, density of states projected from atom's orbit and charge concentration in space. The exploration of these critical physical characteristics generate distinct physical and electrical properties of the distinct material Silicon doped graphene (Si:Gr) permitting it to be used in semiconductor technology [1]. Due to the excellent carrier mobility and saturation velocity, graphene devices are very useful in RF applications. Recent studies suggest that utilizing bare silicon as a supporting substrate without an insulating layer under the graphene channel in conventional field effect transistor (FET), can result in high output resistance and voltage gain, which provides higher cut-off frequency comparing with conventional graphene-FET (GEFT) [2]. In this work, an N-channel GFET with printed channel length of 50nm has been designed with Si:Gr as channel material and the Si:Gr is deposited on lightly doped p-type silicon substrate eliminating the insulator layer. For optimum RF performance bottom gate with SiO<sub>2</sub> as gate dielectric has been utilized. The device has provided maximum cut-off frequency of 496GHz and lon/loff ratio of 139.5x10<sup>3</sup> (bottom gate, metallic contact) proposing a novel device for RF and logic circuit applications.

### References

- [1]. D. Nguyen, N. Tran et al., Nature, 2020, Available: 10.1038/s41598-020-68765-x

- [2]. S. Song, J. Bong et al., Nature, 2016, Available: 10.1038/srep25392

- [3]. Saeed S. Azadeh et al, IEEE, 2011 DOI: 10.1049/mnl.2011.0195

- [4]. Min S. Janga et al, PNAS, 2013, <u>https://doi.org/10.1073/pnas.1305416110</u>

- [5]. J. S. Moon et al., IEEE Electron Device Lett., vol. 31, no. 4, pp. 260–262, Apr. 2010

- [6]. Y. Lin et al. ACS Publications, 2009, Available: 10.1021/nl803316h

### **Figures**

Figure01: (left) Theoretical structure of proposed device<sup>2</sup> (middle) simulated device (right) IV characteristics of the device at VDS = 0.2V

Figure 02: Transconductance vs gate voltage, Output conductance vs drain voltage and gate capacitance of the proposed device. Successful results verify the validity of the proposed device design.