## Two-Dimensional Materials for Digital Electronics Beyond the 1 nm Technology Node

## Tomás Palacios

Jiadi Zhu, Yixuan Jiao, Hae Won Lee, Peng Wu, Tianyi Zhang, and Jing Kong Massachusetts Institute of Technology, 77 Massachusetts Ave, Bldg. 39-567, Cambridge, MA 02139 tpalacios@mit.edu

The thickness of logic transistor channels needs to be drastically reduced as the lateral dimensions of Silicon transistors go below 1 nm technology node, to be able to pack more devices in smaller chips, increase their operating frequency and reduce their power consumption. Unfortunately, interface roughness severely reduces the carrier mobility when the transistor channel is thinned below 2 nm. In addition, the bandgap of silicon is too small to limit the leakage current.

This talk will summarize some of the work that our group at MIT has been doing to demonstrate the feasibility of using two-dimensional (2D) layered materials as the semiconducting channel in devices below 1 nm technology node. Molybdenum disulphide (MoS<sub>2</sub>) for n-type channel transistors, and either tungsten diselenide (WSe<sub>2</sub>) or tungsten disulphide (WS<sub>2</sub>) for p-type channel transistors have ideal material properties to address some of the key challenges in future digital electronics [1]. Recent advances in material synthesis [2], key process modules [3] and device integration [4] will be discussed, as well as a calibrated design-technology co-optimization (DTCO) study.

Acknowledgments. - This work has been partially funded by the SRC JUMP 2.0 SUPREME and CHIMES Centers, the MIT-ARO Institute for Soldier Nanotechnologies, NSF Convergence Phase 2 program, and the ARO Ultra Wide Bandgap 2D Materials program.

## References

- Yu, L., Zubair, A., Santos, E. J. G., et al. High-Performance WSe<sub>2</sub> Complementary Metal Oxide Semiconductor Technology and Integrated Circuits. Nano Lett., 15, 8, 4928-4934 (2015).

- [2] Zhu, J., Park, JH., Vitale, S.A. et al. Low-thermal-budget synthesis of monolayer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform. Nat. Nanotechnol. 18, 456–463 (2023).

- [3] Shen, PC., Su, C., Lin, Y. *et al.* Ultralow contact resistance between semimetal and monolayer semiconductors. *Nature* **593**, 211–217 (2021).

- [4] Wu, P., Zhang, T., Zhu, J. et al. 2D materials for logic device scaling. Nat. Mater. 23, 23–25 (2024).

## Figures

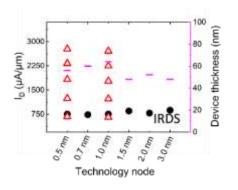

**Figure 1:** Simulations of the ON state current as a function of the number of MoS<sub>2</sub> channels for different technology nodes (red triangles). The minimum current levels per channel according to the International Roadmap for Devices and Systems (IRDS) are shown in black circles, together with the maximum height allowed per device (magenta lines).