## Inkjet-printed low-dimensional materials-based complementary electronic circuits on paper

## Elisabetta Dimaggio<sup>1</sup>

Irene Brunetti<sup>1</sup>, Lorenzo Pimpolari<sup>1</sup>, Silvia Conti<sup>1</sup>, Robyn Worsley<sup>2</sup>, Subimal Majee<sup>2</sup>, Dmitry K. Polyushkin<sup>3</sup>, Matthias Paur<sup>3</sup>, Giovanni Pennelli<sup>1</sup>, Giuseppe Iannaccone<sup>1</sup>, Massimo Macucci<sup>1</sup>, Francesco Pieri<sup>1</sup>, Thomas Mueller<sup>3</sup>, Cinzia Casiraghi<sup>2</sup>, Gianluca Fiori<sup>1</sup> <sup>1</sup>Dipartimento di Ingegneria dell'Informazione, University of Pisa, Pisa, Italy <sup>2</sup>Department of Chemistry, University of Manchester, Manchester, UK <sup>3</sup>Institute of Photonics (TU Wien), Vienna, Austria <u>elisabetta.dimaggio@unipi.it</u>

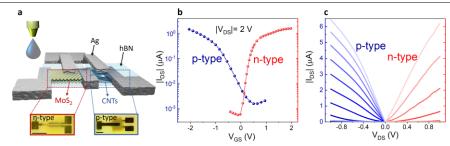

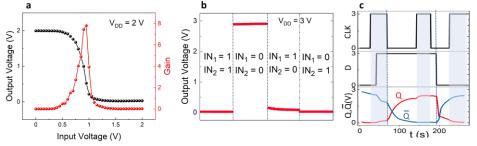

At the dawn of the flexible and wearable electronics age, the seek for new materials enabling the integration of complementary metal-oxide-semiconductor (CMOS) technology on flexible substrates finds in low-dimensional materials (either 1D or 2D) extraordinary candidates. Together with their excellent electrical and mechanical properties, low-dimensional materials are solution processable and suitable to be costeffectively deposited using high-throughput techniques, compatible with direct printing on different flexible substrates [1]. Here, we report an inkjet-printed CMOS-like technology on paper, combining *n*-type MoS<sub>2</sub>-based and *p*-type carbon nanotubes (CNTs)-based field effect transistors (FETs) with hBN dielectric (Figure 1a). Both types of printed transistors exhibit good performances in terms of mobility (in the order of 10 cm<sup>2</sup>/Vs) and ON/OFF current ratio (> 10<sup>3</sup>), and their characteristics can be matched adjusting the channel dimensions (Figures 1b, c) [2]. The proposed devices have been successfully used to design and fabricate some fundamental CMOS building block, such as low-voltage inverters (Figure 2a), NOR gates (Figure 2b) and D-latches (Figure 2c), showing a path for the fabrication of efficient CMOS circuits for cost-effective applications.

## References

- [1] F. Bonaccorso et al., Advanced Materials vol. 28 (2016), 6136-6166

- [2] I. Brunetti et al., npj 2D Materials and Applications vol. 5, (2021), 85.

Figures

Figure 1: a) Sketch of the proposed CMOS-like circuit, together with the input (b) and output (c) characteristics of a p-type and a n-type FET.

**Figure 2:** a) Input-Output characteristic (left axis) and voltage gain (right axis) of an inverter. b) Output voltage of a NOR gate as a function of the input states. c) Time evolution of the output, Q and /Q, as a function of the input signal, D, and clock, CLK.

## Graphene2022