# Pinch-off resistance and Schwinger effect in hBN-encapsulated GFETs

## Aurélien Schmitt<sup>1</sup>

David Mele<sup>1</sup>, Wei Yang<sup>2</sup>, Mark Oliver Goerbig<sup>3</sup>, Christophe Voisin<sup>1</sup>, Jean-Marc Berroir<sup>1</sup>, Gwendal Fève<sup>1</sup>, Emmanuel Baudin<sup>1</sup> and Bernard Plaçais<sup>1</sup>

<sup>1</sup>Laboratoire de Physique de l'Ecole Normale Supérieure, 24 rue Lhomond, 75005 Paris <sup>2</sup>Beijing National Laboratory for Condensed Matter Physics, Beijing, 100190 <sup>3</sup>Laboratoire de Physique des Solides, Univ. Paris-Sud, Université Paris Saclay, 91405 Orsay

#### aurelien.schmitt@phys.ens.fr

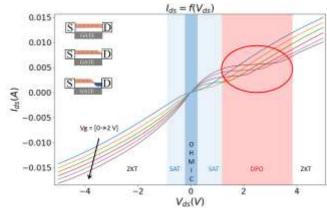

Electronic transport in hBN-encapsulated graphene field effect transistors (GFETs) has already been characterized in details. [1] With increasing bias, the ohmic regime is first superseded by a velocity saturation regime due to electron scattering with optical phonons of hBN and graphene. Then, further increasing the bias leads to the appearance of an interband current due to Zener-Klein tunneling [2]. These phenomena are well-established in the doped regimes. (Figure 1, negative bias region)

However, near charge neutrality, we cannot ignore that the potential drop along the channel results in non-uniform chemical potential and doping profiles. inhomogeneities play a critical role and give birth to peculiar transport properties at large bias. [3] As an illustration, in semiconductor MOSFETs, the application of a large bias nucleates an electronic depletion in the channel at the drain electrode. graphene, a Dirac pinch-off (DPO) occurs as well, but the depletion region is limited due to the absence of gap. (See illustrations on fig. 1, and positive bias region)

We report on the room-temperature experimental study of a high mobility hBN-encapsulated GFET with a close graphite backgate. The DPO occurs when the gate and drain voltages are equal, resulting in a zero charge carrier density at the drain side. At DPO, we observe a current plateau with bias which corresponds to a differential resistivity peak. Surprisingly, we observe that the resistance peak increases by two orders of magnitude (resistivity  $600\Omega \rightarrow 50M\Omega$ ) when increasing the gate voltage. This points to

the formation of an insulating phase in the DPO region (~ 40nm) with electric fields around 10<sup>8</sup> V/m. At larger bias, an exponentially fast decrease occurs when reaching the bipolar regime.

Robust scalings are demonstrated: when approaching the DPO they point to a special relativity interpretation, whereas beyond the DPO, they correspond to the Schwinger particle-antiparticle pair creation formula. In this last regime, the Schwinger theory quantitatively predicts the correct exponential resistance decay with bias. These observations suggest that the Dirac Pinch-off regime is analogue to the breakdown of a relativistic vacuum in QED.

### References

- [1] I. Meric, et al "Current saturation in zerobandgap, top-gated graphene field-effect transistors." Nat. Nanotech. 3, 654 (2008)

- [2] W. Yang, et al "A Graphene Zener–Klein Transistor Cooled by a Hyperbolic Substrate." Nat. Nanotech. 13, 47 (2018)

- [3] Q. Wilmart, et al "High-Frequency Limits of Graphene Field-Effect Transistors with Velocity Saturation." Appl. Sci. 10(2), 446 (2020)

## **Figures**

**Figure 1:** Experimental I-V curves of the GFET at various gate voltages showing the different transport regimes: ohmic behaviour, velocity saturation (SAT), Zener-Klein tunnelling (ZKT), and Dirac Pinch-off (DPO) in the positive bias region. Inset shows the doping profiles along the channel before DPO, at DPO and after DPO with positive doping (resp. negative) in red (resp. blue)