## Scalable process of high quality graphene for integration into electronic circuits.

## Tymofiy Khodkov<sup>1</sup>

S. Goossens<sup>1</sup>, Yu Bi<sup>1</sup> and F.H.L. Koppens<sup>1,2</sup>

<sup>1</sup> ICFO - The Institute of Photonic Sciences, Av. Carl Friedrich Gauss 3, 08860 Castelldefels, Spain.

<sup>2</sup> ICREA – Institució Catalana de Recerça i Estudis Avancats, 08010 Barcelona, Spain

tymofiy.khodkov@icfo.eu

The development of full wafer-scale integration processes is a "bridge" between lab fabrication techniques and industry production that should eventually bring 2dimentional materials, such as graphene, to applications market-volume such as broadband image sensors and high speed photodetectors. However, to be fully established, this process requires to overcome several drawbacks, including minimizing doping inhomogeneity, hysteresis and the surface roughness. Moreover, high electron mobility is a necessary factor to get ultra-fast and sensitive devices.

Previously it has been demonstrated that the combination of graphene with other atomically flat materials leads to outstanding device performance where carrier mobility reaches values far above 100 000 cm2/Vs at room temperature (RT) [1,2].

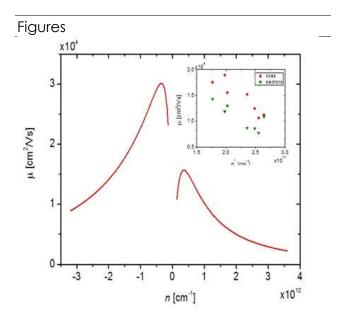

Here show potentially scalable we fabrication methods for hetero-stacking 2D materials, like hexagonal boron nitride (hBN) and transition metal dichalcogenides (TMD), with CVD graphene for low-doped high mobility devices at RT. We developed a novel post-process temperature treatment to recover intrinsic quality of graphene after a detrimental wet transfer. The device mobility of commercially available, wet transferred CVD graphene reaches values above 20 000 cm2/Vs (Fig.1). Besides, the study involves integration of large area graphene onto chemically grown other 2D materials on insulating substrates. Making a clean interface between graphene and

other 2D material plays an important role for high-quality two-dimensional devices. We also propose one of the subsequent multistacking transfer method inside a vacuum chamber, which makes it possible to reduce surface contaminations and create 2D hetero-structures with flat and residual-free interfaces.

Reliable wafer-scale graphene transfer methods allows further implementation of devices in the CMOS technology platform[3]

## References

- [1] F. Pizzocchero et al., Nature Comm. 7, 11894 (2016).

- [2] D. G. Purdie et.al, Nature Comm. 9, 5387 (2018).

- [3] S. Goossens et al., Nat Phot. 11, 366–371 (2017).

**Figure 1:** Room temperature field effect mobility of wet transferred CVD graphene with thermal post-treatment encapsulated between hBN flakes. The inset shows correlation between mobility and residual doping n\* for CVD graphene on hBN for various samples