# 'Monolayer' tungsten oxide as a strong p-dopant for graphene

### Min Sup Choi<sup>a,b</sup>

Younghun Jung<sup>a</sup>, Ankur Nipane<sup>a</sup>, Abhinandan Borah<sup>a</sup>, Bumho Kim<sup>a</sup>, Myeongjin Lee<sup>b</sup>, Won Jong Yoo<sup>b</sup>, James Hone<sup>a</sup>, James Teherani<sup>a</sup>

°Columbia University, 550 W 120<sup>th</sup> Street, New York, NY, 10027, USA

<sup>b</sup>SKKU Advanced Institute of Nano Technology, Sungkyunkwan University, 2066 Seobu-ro, Suwon, 16419, Korea

## mc3614@columbia.edu

# Abstract

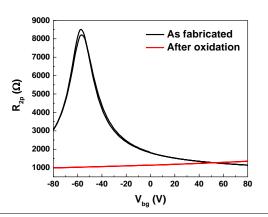

Though graphene has been extensively studied for the past decade for applications in high speed electronics due to its extremely high carrier mobility [1], its high conductivity relative to its atomic-layer thickness also creates opportunities for its use as a transparent electrode. The use of graphene in these applications requires the development of reliable doping methods. There have been many studies of graphene doping techniques that use electrostatic chemical adsorption, molecular force, doping, annealing, UV, plasma treatment, among other methods. [2] Many of these techniques have trade-offs such as process damage, dopant instability, and poor transparency due to thick polymer coatings. Thus, we seek to develop a doping technique that preserves graphene's atomic structure, transparency, and yields high conductivity. Here, we develop an atomic-layer of p-type doping for graphene using 'monolayer' WO<sub>x</sub>, which is formed by the room-temperature UV-ozone oxidation of monolayer WSe<sub>2</sub>. To demonstrate the technique, a back-gated graphene FET was fabricated with a top layer of monolayer WSe<sub>2</sub>. The device was measured before and after room-temperature UV-ozone oxidation, and the results are shown in Figure 1. The conversion from WSe<sub>2</sub> to WO<sub>x</sub> strongly ptype dopes the graphene as evidenced by missing Dirac peak in the measured range and the reduced resistance. This work demonstrates the potential of 'monolayer'  $WO_x$  as a p-type dopant for graphene for use in electronics as well as a transparent electrode.

## Acknowledgement

This work was supported by Global Research Laboratory (GRL) program (2016K1A1A2912707) and Research Fellow program (2018R1A6A3A11045864) funded by the National Research Foundation of Korea (NRF). This work was also supported by the National Science Foundation through ECCS-1752401 and the Center for Precision Assembly of Superstratic and Superatomic Solids (DMR-1420634).

#### References

- P. Avouris, F. Xia, MRS Bulletin, 37 (2012) 1225-1234

- [2] H. Lee, K. Paeng, I. S. Kim, Synthetic Metals, 244 (2018) 36-47

#### Figures

**Figure 1:** Two-probe resistance as a function of back-gate voltage for a graphene FET. Channel length and width are 5 and 1.5 um, respectively. The two curves correspond to an as-fabricated device of monolayer graphene with a top layer of monolayer WSe2 and the device after oxidation of WSe<sub>2</sub> layer.