## A novel and fast route to reduce Graphene oxide thin-film on wafer-scale

## Walid-M. Munief\*1,2

Xiaoling Lu<sup>3</sup>, Yannick Lang<sup>2</sup>, Jannick Wilhelm<sup>1</sup>, Anette Britz<sup>2</sup>, Vivek Pachauri<sup>3</sup>, Rolf Hempelmann<sup>5</sup>, Michael Schmitt<sup>4</sup>, Sven Ingebrand<sup>1,3</sup>

1)Ram Group DE GmbH, Amerikastrasse 15, 66482 Zweibrücken, Germany

2) Department of Informatics and Microsystem Technology, University of Applied Sciences Kaiserslautern, Amerikastrasse 1, 66482 Zweibrücken, Germany

3) Institute of Materials in Electrical Engineering 1, RWTH Aachen University, Sommerfeldstrasse 24, 52074 Aachen, Germany

4) Institute for Coatings and Surface Technology, University of Applied Sciences Niederrhein, 47805 Krefeld, Germany

5) Transfercentre Sustainable Electrochemistry, Saarland University and KIST Europe, Campus Dudweiler Zeile 3, 66125 Saarbrücken, Germany

\*<u>Corresponding author</u>: Walid\_Munief@yahoo.de

A spin-coating process to create graphene oxide (GO) thin films with precise thickness control over silicon and glass wafer was successfully established. A suitable reduction treatment transformed GO into reduced graphene oxide (rGO), which serve as highly sensitive bipolar transducer layers in the biosensing field.

As a starting material we optimized the exfoliation synthesis. To reach a reliable quality of GO as a nanomaterial source for the spin coating, the temperature parameter during synthesis was lowered and additional purification steps were added. The spin-coating on pre-treated wafers with uniform siloxane lavers enabled us to generate homogeneous GO films on wafer-scale. Subsequently, the GO were structured into micro- and nanoscale patterns by standard photolithography or nano-imprint pattering.

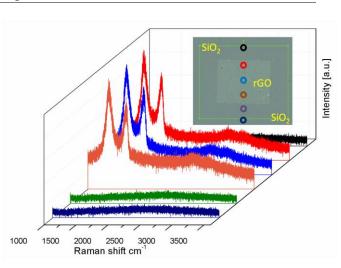

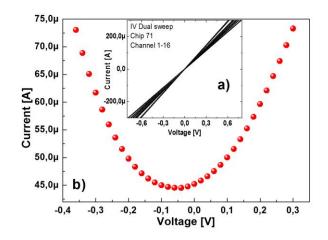

Towards process integration of the GO, a novel and fast reduction method was realized by Rapid Thermal Processing (RTP). The evolution of the reduction process was confirmed by characterization Fig.1). The I-V Raman measurements in Fig 2.a) showed that the sheet resistance of the rGO on interdiaitated microelectrodes was in the range of 3-40  $k\Omega$ after RTP reduction treatment for 2s. The bipolar field-effect in Fig 2.b) illustrate the Dirac point between -0.1 V and 0 V. The position of the characteristic curve shows an n-type behave which was induced only by the reduction temperature at 350°C.

## References

[1] Lu & Munief, Front-End-of-Line Integration of Graphene Oxide for Graphene-Based Electrical Platforms. Advanced Material Technologies. 1700318, (2018). Figures

**Figure 1:** The mapping technique combined with the Raman spectroscopy allows a precise determination of the coated and structured 1-2 nm thick GO layer.

**Figure 2:** a) The I-V proves the ohmic contact of the rGO thin film and the IDE after RTP reduction. b) In DC-mode the characteristic bipolar function of rGO ISFET in 10 mM PBS buffer.

Towards process integration of the GO, a novel and fast reduction method was realized by Rapid Thermal Processing (RTP). Controlled process time for thermal reduction in combination with a fast annealing step as well as selectable temperature regimes were identified as the key factors to minimize the electrical variation and the sheet resistance for the rGO coating.