## Synthesis of epitaxial graphene on SiC for graphenebased electronics

Alberto García-García<sup>1,2</sup>, Ana Ballestar<sup>1</sup>, Luis Serrano-Ramón<sup>1</sup>, Gemma Rius<sup>2</sup>, Manuel Ricardo Ibarra<sup>3</sup>, José María De Teresa<sup>3,4</sup>, Philippe Godignon<sup>2</sup>

<sup>1</sup> Graphene Nanotech (GPNT), CEMINEM, Zaragoza, Spain

<sup>2</sup> Instituto de Microelectrónica de Barcelona, CNM-CSIC, Barcelona, Spain

<sup>3</sup> Lab. de Microscopías Avanzadas (LMA), Instituto de Nanociencia de Aragón (INA), Depto. de Física de la Materia Condensada, University of Zaragoza, Zaragoza, Spain

<sup>4</sup> Instituto de Ciencia de Materiales de Aragón (ICMA), CSIC-University of Zaragoza, Zaragoza, Spain

alberto@gpnt.es

Despite outstanding electronic properties of graphene such as high carrier mobility and ballistic transport at room temperature [1], wafer-scale synthesis of high-quality graphene still remains a major bottleneck for mass production of marketable graphene-based devices.

Within this framework, controlled synthesis of epitaxial graphene (EG) on silicon carbide (SiC) wafers [2], via the preferential sublimation of Si surface atoms at high temperatures (typically > 1500°C), or, alternatively, catalytic growth by chemical vapour deposition (CVD) constitute the only realistic approaches for the commercial success of innovative graphene electronic devices.

Competitive advantage of EG on SiC for electronics include SiC intrinsic properties [3], i. e. wide bandgap, high-breakdown electric field, good thermal conductivity and high saturated electron drift velocity. SiC constitutes an ideal platform to fabricate high-voltage devices, microwave power field effect transistors (FETs) and integrated circuits (ICs) operating at high temperature. Remarkably, the so-called graphitization of SiC does not require subsequent transfer process, preventing e.g. metallic/nonmetallic contamination. In other words, EG directly grown on SiC is a compatible process with standard complementary metal-oxide semiconductor (CMOS) technology.

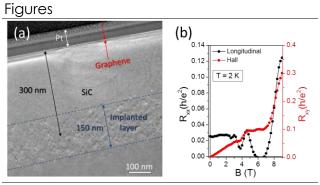

In this contribution, we will summarize our findings on the synthesis of EG on SiC. Emphasis will be given to our advances for its subsequent processing, e.g. for the fabrication of back-gated graphene transistors. Offered strategies include a buried implanted layer SiC, on at controllable depth and avoiding severe surface lattice damage (Fig. 1); or using a semi-insulating thin SiC seed-layer, fabricated on top of doped wafers via homoepitaxial growth.

References

- [1] K. S. Novoselov et al., Nature, 490 (2012) 192

- [2] N. Camara *et al.*, Appl. Phys. Lett. 93 (2008) 263102

- [3] M. Östling et al., IEEE 23 International Symposium on Power Semiconductor Devices and ICs (2011) 10

Figure 1: (a) Cross-sectional transmission electron microscopy image of an ion (nitrogen) implanted SiC substrate covered with an EG layer; (b) Longitudinal ( $R_{xx}$ ) and Hall ( $R_{xy}$ ) resistances as a function of the magnetic field at 2 K.