## High Electrical Field Carrier Transport in Black Phosphorus Field Effect Transistor

Faisal Ahmed<sup>1</sup>, Min Sup Choi<sup>2</sup>, Young Duck Kim<sup>3</sup>, James Hone<sup>3</sup> and Won Jong Yoo<sup>1,2,\*</sup>

<sup>1</sup>School of Mechanical Engineering, Sungkyunkwan University, Suwon, Korea.

<sup>2</sup>Department of Nano science and Technology, Sungkyunkwan University, Suwon, Korea.

<sup>3</sup>Department of Mechanical Engineering, Columbia University, New York, USA.

yoowj@skku.edu

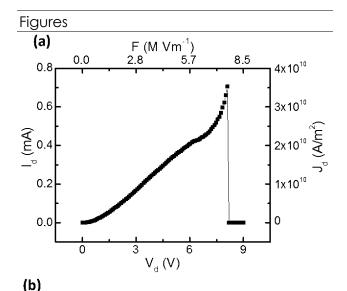

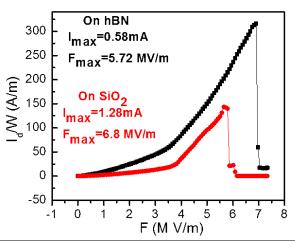

Layered black Phosphorus (BP) is emerged as a favourable candidate material for use in solid state electronics and opto-electronics applications due to its intriguing properties.[1,2] Most of the previous studies on two-dimensional (2D) semiconducting materials in general and BP in particular are mainly focused towards low electrical field and low temperature measurements to understand their inherent carrier transport. [1-3] However, in practice these devices are operated at harsh environment conditions like higher applied electrical field and temperature. Therefore, we applied high electrical field to the BP devices and observed a record high current density of 3×10<sup>10</sup> A/m<sup>2</sup> with an electrical field endurance of 7 MV/m on SiO<sub>2</sub> substrate before Joule breakdown, that was primarily caused by deposition of thermal energy along BP-SiO<sub>2</sub> interface. Furthermore, three times enhancement in power density and 13% increase in breakdown temperature of BP device is realized by using 2D hBN as a substrate instead of thermal resistive SiO2, due to better structural and thermal compatibility of hBN with BP. Interestingly, we observed unusual phenomenon of multiplication due to the impact ionization of charged carriers instead of commonly observed current saturation at higher applied electrical field in all of our fabricated BP devices on 300nm thick SiO<sub>2</sub> findings substrate. These are highly significant to realize reliable and energy efficient devices and circuits based on 2D materials.

## References

- [1] L. Li et al., Nat. Nanotechnol., 9, 2014, 372.

- [2] H.-M. Li et al., Nat Commun., 6, 2015, 6465.

- [3] D. Yue, et al., Nanoscale, 8, 2016, 12773.

- [4] E. Pop, Nano Research, 3, 2010, 147.

**Figure a:** High electrical field breakdown of 8nm thick BP device at zero gate bias.

**b:** Comparison of electrical breakdown of BP devices on SiO<sub>2</sub> and hBN substrates.

## **ACKNOWLEDGEMENTS**

This work was supported by the Global Research Laboratory (GRL) Program (2016K1A1A2912707) and Global Frontier R&D Program (2013M3A6B1078873) at the Center for Hybrid Interface Materials (HIM), both funded by the Ministry of Science, ICT & Future Planning *via* the National Research Foundation of Korea (NRF).